# Simulation Analysis of 2-D Discrete Wavelet Transform by using Modified Radix-4 Booth Multiplier

Mr. Hemantkumar H. Nikhare<sup>1</sup>, Prof. Ashish Singhadia<sup>2</sup>

M.Tech Scholar, Digital Communication, VIT, Bhopal, India<sup>1</sup>

Professor, Electronics & Tele (Department), VIT, Bhopal, India<sup>2</sup>

Abstract: A new architecture namely 2-D DWT, Multiplier-and accumulator (MAC) based Radix-4 Booth Multiplication Algorithm for high-speed arithmetic logics have been proposed and implemented on Xilinx. By combining multiplication with accumulation and devising a hybrid type adder the performance was improved. The modified booth encoder will reduce the number of partial products generated by a factor of 2. Fast multipliers are essential parts of digital signal processing systems. The speed of multiply operation is of great importance in digital signal processing as well as in the general purpose processors. The number to be added is the multiplicand, the number of times that it is added is the multiplier, and the result is the product. Each step of addition generates a partial product. the simulation is done on the Modelsim and finally output is analysed by using Matlab.

Keywords: - VLSI, Carry Select Adder (CSA), Carry Look Ahead Adder (CLA), ASM

#### **1. INTRODUCTION TO DWT**

of choice at the heart of recent image compression bank structure. algorithms. Adopted by the JPEG 2000 image compression standard [1], it significantly outperforms metrics such as throughput and latency while filter algorithms based on other transforms, such as the discrete coefficient quantization impacts the signal processing cosine transform, in terms of objective metrics as well as properties of the filter bank and determines its image perceptual image quality [2]. The success of the DWT stems from its ease of computation and its inherent the filter bank determines properties such as latency and decomposition of an image into non-overlapping subbands that enables the design of efficient quantization algorithms and allows for incorporation of the human visual system.

A DWT based image codec is a good choice for applications such as remote exploration, urban search and rescue operations and satellite imaging. These applications require transmission of still images from remote image acquisition devices to base stations. Images are compressed after acquisition to reduce the number of data bits that need to be transmitted back to the base station over a wired or wireless communication channel. A good hardware codec employed in these applications will have: low latency and high throughput if real-time operation is desired, low power consumption if working in an representations. untethered, battery-driven environment, small hardware size, and most importantly, high fidelity for the The number of non-zero terms in the SPT representation reconstructed image after compression. This wavelet has of a coefficient, denoted by T, provides an estimate of the been shown to possess properties favorable for image hardware cost associated with implementing the compression; part I of the JPEG 2000 standard specifies coefficient. this wavelet for lossy compression. The DWT is typically computed using a perfect reconstruction (PR) filter bank. The performance of an FPGA implementation of the filter distortion PR condition and, consequently, image bank depends on the following two implementation design issues:

1. the filter bank structure and filter coefficient quantization; and,

The Discrete Wavelet Transform (DWT) is the transform 2. the hardware architecture used to implement the filter

The filter bank structure determines hardware compression performance. The hardware architecture of power consumption. This thesis investigates the first issue of filter bank implementation, namely, filter bank structure and coefficient quantization. The image compression performance of the filter bank implementation critically depends on the two perfect reconstruction (PR) conditions: the no-distortion condition and the no aliasing condition.

When the irrational coefficients of the biorthogonal 9/7 wavelet filters are implemented in a floating point format, both PR conditions are satisfied and the filter bank gives perfect reconstruction under lossless compression. Multiplication is then achieved by shifting and adding. Thus, the filter coefficients have to be quantized, i.e. approximated by fixed point SPT

This quantization of the filter coefficients alters the nocompression performance is affected. the closer the quantized filter coefficients are to the un quantized coefficients, and the closer the quantized compression performance is to the un quantized performance. However,

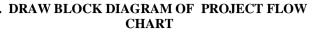

more non-zero terms means higher hardware cost. 3. DRAW BLOCK DIAGRAM OF PROJECT FLOW Conversely, fewer non-zero terms means lower hardware cost, but worse compression performance. Thus there is a trade-off between hardware cost and compression performance.

The filter bank structure also influences the performance of the filter bank. Cascade filter structures are more immune to coefficient quantization than direct structures and, in general result in better compression performance for the same T.

Furthermore, polyphase structures operate at higher clock speeds than non-polyphase structures and hence result in better throughput. The lifting structure an alternative to the traditional filter bank structure offers the advantage of an orthogonal implementation that is more robust to coefficient quantization.

All three structures are evaluated in terms of compression performance (using peak signal-to-noise ratio PSNR) and various hardware metrics.

For each structure, optimal quantized values are found for the filter coefficients. These coefficients enable the implementation of a fast, multiplier less DWT codec that generates the best possible PSNR performance for the given structure.

#### **2. OVERVIEW**

In this thesis we used image processing using VHDL the algorithm for image compression using DWT and modified Radix-4 Booth algorithm for reducing the delay time for execution of the process and to reduce the storage space in hard disk.

Image is taken as an input using Matlab and 1. generating the matrix of row and columns up to quantization levels [256, 256] row and column.

The entity is generated of the input image in 2. VHDL coding by creating 'Do file' for execution in Modelsim VHDL coding.

3. Modified Booth algorithm is applied on the input image strings rows and columns to get the partial products as output of image in VHDL coding in Modelsim.

Booth algorithm used as a Multiplier to generate 4 the partial products. Application of Multiplier to enhances the speed of execution and creating a less storage space for the execution of programme.

The final output of Booth algorithms partial 5. products are used as a input to DWT for image compression technique.

The output resultant matrix elements or Pixels of 6. DWT is simulated on MATLAB to obtained corresponding output compressed image.

The Compressed Output Image generated is in 7. Grev Scale Format.

8 Output image is also analysed by using Haar wavelet Transform.

Fig. 1. Block Diagram of Project

### 4. DETAILS OF BLOCK DIAGRAM

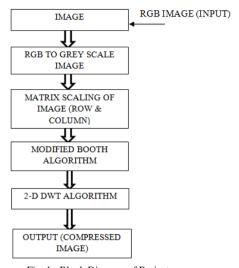

Fig 1(a). Design of Architecture of DWT

#### 5. OVERVIEW OF DWT:

1-D DWT stands for one dimensional discrete wavelet transform. It is a transform similar to discrete fourier transform(DFT). It uses multi-resolution technique for time-frequency analysis of signals. The main advantage of DWT compared to DFT is that we get both time and frequency analysis of a signal at the same time. The DWT is mainly used for image compression. It also has various signal processing applications. The DWT can provide significant compression ratios than the previous techniques like the Discrete Cosine Transform (DCT) and the Discrete Fourier Transform(DFT). The signal to be analyzed is passed through low pass and high pass filters. This is then followed by decimation by two. This yields

the low pass sub-bandyL and the high pass sub-bandyH. Stage 1(a) - DWT coefficients To reconstruct the original signal we first do interpolation • Input: 8 bit pixels, Output: DWT coefficients - 16 bits followed by low pass and high pass filtering. This is • 2 pixels/WORD, 512 Rows and 256 Columns, 0.5 MB illustrated in the figure below.

#### 5.1 Wavelets Multi-resolution analysis:

• Example: consider the sequence of pixels: 10 8 1 3 5 7 8 6

averages: [9 2 6 7] differences: [-2 2 2 -2]

averages: [5.5 6.5] differences:[-7 1]

averages: [6] differences: [1]

• Each stage divides the band into 2 subbands - low frequency + high frequency

coefficients

· Regions of discontinuities will have large coefficients, smooth regions will

have smaller differences

• Error introduced by truncating a coefficient is proportional to its magnitude,

can truncate small coefficients without considerable distortion

#### 5.2. 1-D DWT for Image Compression:

• DWT coefficients of input image - multiple levels of wave-letting

· Coefficients are quantized - coefficients in each subband is quantized

separately

· Coefficients are zero thresholded, different subbands have different

thresholds

· Longs spells of zero are run length encoded

• The coefficients are then entropy encoded

## **5.3 DWT Algorithm:**

#### **A)Design Specification**

• Input image: 512x512 pixel, gray scale frame, 8 bits/pixel

· Support 3 different configurations of encoder with varying

levels of compression

### **B)Design Partition - 2 stages**

- Stage 1: DWT coefficients over 3 stages of wave-letting

- Stage 2: Dynamic Quantization,

- Zero thresholding,

- RLE of zeroes and,

Entropy encoding of DWT coefficients

2 stages are implemented on 2 separate PEs

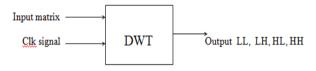

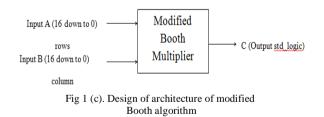

Fig 2. Stages of implementation

• From 512 pixels in a row, extract 256 low frequency coefficients + 256 high frequency coefficients

· Symmetric extension at the boundaries

Fig 2(b). Design Partition on stage 1 of length 512

#### Stage 1(b) - DWT coefficients

• Extend same scheme of interleaved memory access along Y direction

But now the 2 values obtained in a READ are not consecutive pixel values of a column

rather they are one pixel each of two parallel columns 3 stages of Wave-letting

- Stage 1 On rows and columns of length 512

- Stage 2 On rows and columns of length 256

- Stage 3 On rows and columns of length 128 Input Data Coefficient data

| a0     | ьо         | <b>f0</b>      | <i>f</i> 0<br>₅ |

|--------|------------|----------------|-----------------|

| a1     | ы          | <b>g</b> 0     | <b>g0</b>       |

| a2     | <b>b</b> 2 | <b>f1</b><br>a | <b>f</b> [1]    |

|        |            | <b>g1</b>      | <b>g1</b>       |

| *<br>* |            |                | *<br>*          |

| a510 | Ь510        | f255 f | 255 |

|------|-------------|--------|-----|

| a511 | <b>b511</b> | g255 g | 255 |

Fig 2(c). Design Partition on stage 2 of length 256

| 0 | 2 | 5 |   |  |  |  |  |

|---|---|---|---|--|--|--|--|

| 1 | 3 | ſ | 8 |  |  |  |  |

|   | 4 | 6 | 0 |  |  |  |  |

|   | 7 | 7 | 9 |  |  |  |  |

Fig 2 (d). Design Partition on stage 3 of length 128

# 6. WHY ADAPTIVE IMAGE COMPRESSION?

Image processing systems can encode raw images with different degrees of precision, achieving varying levels of The modified Booth algorithm minimises the number of compression. Encoding can be achieved with different encoders with varying compression ratios. The need to dynamically adjust the compression ratio of the encoder arises in many situations. One example involves the realtime transmission of encoded data over a packet switched network. On detecting network congestion, the encoder can cut down the precision and gain more compression, rather than waiting for some packets to be dropped. To suitably adapt the encoder to the varying compression requirements, adaptive adjustments of the compression parameters are required. This involves reconfiguring the encoder in some sense.

#### 7. RADIX-4 BOOTH MULTIPLIER

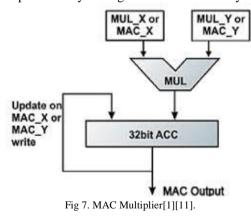

With the help of recent advances in multimedia and communication systems, real-time signal processing like audio signal processing, video/image processing, or large capacity data processing are increasingly being demanded. The multiplier and multiplier-and-accumulator (MAC) are the essential elements of the digital signal processing such as filtering, convolution, and inner products. Most digital signal processing methods use nonlinear functions such as discrete cosine transform (DCT) or discrete wavelet (DWT). transform because thev are basically accomplished by repetitive application of multiplication and addition. Booth recoding is a technique for high speed multiplication, by recoding the bits that are multiplied. The number of partial products reduced to half, using the technique of radix-4 Booth recoding [1],[2][6].

#### 7.1 Algorithm:

Modified Radix-4 Booth's Algorithm is made use of for fast multiplication. The salient features of this algorithm are:

• Only n/2 clock cycles are needed for n-bit multiplication as compared to n clock cycles in Booth's algorithm.

• Isolated 0/1 are handled efficiently.

• For even n, the two's complement multipliers are handled automatically whereas for odd n an extension of sign bit is required. Procedure: For all odd values of *i* where i ranges from 1 to n-1 for n-bit multiplication (assuming n is even), the bits of the multiplicand are recoded using the formula.

$y_i = x_i - 1 + x_i - 2 - 2x_i$  ...... (1)

Then multiplication is done in normal way with the yi that have been calculated. The following example illustrated the whole procedure

| A           |      |   | 01              | 00  | 01              |    |    | 17                 |

|-------------|------|---|-----------------|-----|-----------------|----|----|--------------------|

| X           | х    |   | 11              | 01  | 11              |    |    | -9                 |

| Y           |      |   | $0\overline{1}$ | 10  | $0\overline{1}$ |    |    | recoded multiplier |

|             |      |   | -A              | +2A | -A              |    |    | operation          |

| Add $-A$    | +    |   | 10              | 11  | 11              |    |    |                    |

| 2-bit Shift |      | 1 | 11              | 10  | 11              | 11 |    |                    |

| Add $2A$    | $^+$ | 0 | 10              | 00  | 10              |    |    |                    |

|             |      |   | 01              | 11  | 01              | 11 |    |                    |

| 2-bit Shift |      |   | 00              | 01  | 11              | 01 | 11 |                    |

| Add $-A$    | +    |   | 10              | 11  | 11              |    |    |                    |

|             |      |   | 11              | 01  | 10              | 01 | 11 | -153               |

|             |      |   |                 |     |                 |    |    |                    |

Fig 3. Modified Radix-4 booth Multiplication

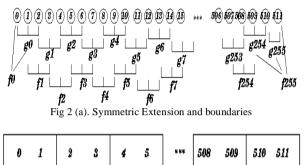

#### 8. RADIX-4 MODIFIED BOOTH MULTIPLIER ALGORITHM

partial products by half. We used the modified Booth encoding (MBE) scheme . It is known as the most efficient Booth encoding and decoding scheme. Τo multiply.multiplicand 'X' by multiplier 'Y' using the modified Booth algorithm. First group the multiplier bits 'Y' by three bits and encoding into one of {-2, -1, 0, 1, 2}. Prior to convert the multiplier, a zero is appended into the LeastSignificant Bit (LSB) of the multiplier. Table I shows therules to generate the encoded signals by MBE scheme and Fig. 2 (a) shows the corresponding logic diagram. The Booth decoder generates the partial products using the encoded signals[1][7].

Fig 4. Basic arithmetic steps of multiplication and accumulation[1],[2][8].

Fig 5. Booth Recoding [2][9].

| Select Line<br>(Encoding) | Partial Products (Operation) |

|---------------------------|------------------------------|

| 000                       | Add 0                        |

| 001                       | Add multiplicand             |

| 010                       | Add multiplicand             |

| 011                       | Add 2* multiplicand          |

| 100                       | Subtract 2* multiplicand     |

| 101                       | Subtract multiplicand        |

| 110                       | Subtract multiplicand        |

| 111                       | Subtract 0                   |

The recoding is done by appending one zero to the Least addition, the signed multiplication based on 2's Significant Bit (LSB) and extending the Most Significant complement numbers is also possible. Bit (MSB) with the sign bit if necessary. Then the grouping of 3 bits from the LSB is done as shown in Fig 2. The obtained result is -1 -1 0 -2. This result is multiplied with the multiplier and the number of partial product is reduced [2][11].

#### 9. VLSI ARCHITECTURE IMPLEMENTATION

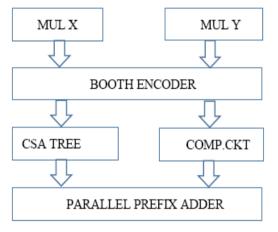

The architecture of the proposed ECAT Booth multiplier is designed by using tree-based carry save reduction followed by parallel-prefix carry-propagate addition architecture. The whole architecture of the proposed ECAT Booth multiplier is shown in Fig.accumulator. In final adder both sum and carry is added to produce the 2N bits product.

Fig 6. VLSI Architecture [2][12].

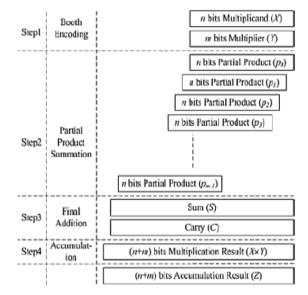

#### **10. ARCHITECTURE OF A MULTIPLIER**

A multiplier can be divided into three operational steps: i. Radix-4 Booth algorithm in which a partial product is generated.

ii. Carry save adder and Accumulator

iii. The final addition in which the final multiplication result is produced by adding the sum and the carry

Generally if N-bit data of multiplicand 'X' is multiplied with N-bit multiplier 'Y' then it generates N- partial products. But if Radix-4 booth algorithm is used then

$$X = -2^{N-1}x_{N-1} + \sum_{i=0}^{N-1} x_i 2^i, \quad x_i \in 0, 1$$

$$X \times Y = \sum_{i=0}^{\frac{N}{2}-1} d_i 2^{2i} Y$$

Where  $di = -2x_{2i+1} + x_{2i} + x_{2i-1}$

$$P = X \times Y + Z = \sum_{i=0}^{N/2-1} di \, 2^i \, Y + \sum_{j=0}^{2N-1} zi \, 2^i.$$

In CSA, the sign extension is used in order to increase the bit density of the operands. Half adder is used to generate sum and carry in CSA. The generated carry is stored in accumulator [1][11].

#### **11. 2-D DISCRETE WAVELET TRANSFORM**

The main challenges in the hardware architectures for 1-D DWT are the processing speed and the number of multipliers and adders while for 2-D DWT it is the memory issue that dominates the hardware cost and the architectural complexity. A 2-D DWT is a separable transform where 1-D wavelet transform is taken along the rows and then a 1-D wavelet transform along the columns. The 2-D DWT operates by inserting array transposition between the two 1-D DWT. The rows of the array are processed first with only one level of decomposition. This essentially divides the array into two vertical halves, with the first half storing the average coefficients, while the second vertical half stores the detail coefficients. This process is repeated again with the columns, resulting in four sub-bands within the array defined by filter output.as in three-level decomposition.

The LL sub-band represents an approximation of the original image, the LL1 sub-band can beconsidered as a 2:1 sub-sampled version of the original image. The other three sub-bands HL1, LH1, and HH1 contain higher frequency detail information. This process is repeated for as manylevels of decomposition as desired. The JPEG 2000 standard specifies five levels ofdecomposition, although three are usually considered acceptable in hardware. In order toextend the 1-D filter to compute 2-D DWT in JPEG2000, two points have to be taken intoaccount. Firstly, the 1-D DWT generates the control signal memory to compute 2-D DWT and managesthe internal memory access. Secondly, we need to store temporary results generated by 2-D column filter. The amount of the external memory access and the area occupied by the embeddedinternal buffer are considered the most critical issues for the implementation of 2-D DWT. As thecache is used to reduce the main memory access in the general processor architectures, in similarway, the internal buffer is used to reduce the external memory access for 2-D DWT. However, theinternal buffer would occupy much area and power consumption. Three main architecture design approaches number of partial products will be reduced to N/2. In were proposed in the literature with the aim to implement

efficiently the 2-D DWT level by level, line-based and block based architectures. These architectures address this difficulty in different ways. A typical level-by-level architecture as uses a single processing module that first processes the rows, and then the columns. Intermediate values between row and column processing are stored in memory. Since this memory must be large enough to keep wavelet coefficients for the entire image, external memory is usually used. Access to the external memory is sometimes done in row-wise order, and sometimes in column-wise order, so high-bandwidth access modes cannot be used. 157 external memory access can become the performance bottleneck of the system for the given J level of decomposition [3][12][14].

#### **12.1 IMAGE ACQUISITION**

Electronic devices such as optical (digital/video) camera, webcam etc can be used to capture the acquired images. In our project we have taken sample picture images. As shown in figure below

Fig 8. Input JPEG Image taken from gallery.

#### 12.2 RGB IMAGE TO GRAY SCALE IMAGE

In photography and computing, a gray scale digital image is a picture within which the worth of every constituent may be a single sample, that's it carries solely intensity data.

Pictures of this kind, additionally celebrated as black-andwhite, are composed exclusively of reminder gray, varying from black at the weakest intensity to white at the strongest . In grey scale pictures, however, we have a tendency to do not completely differentiate however abundant we have a tendency to emit of the different colours we have a tendency to emit the same quantity in every channel. What we will differentiate is that the total quantity of emitted lightweight for every pixel; very little lightweight offers dark pixels and far lightweight is perceived as bright pixels.

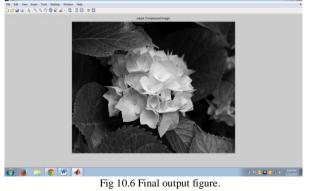

When converting an RGB image to gray scale, we've to require the RGB worth's for every constituent and build as output one value reflective the brightness of that constituent. One such approach is to require the typical of the contribution from each channel: (R+B+C)/3. The red, in experienced and Blue parts square measure separated from the twenty four bit colour worth of every constituent (i,j) to calculate the eight bit grey worth victimization the formula. The Fig. below shows the gray scale image.

#### 12.3 INSERT BLACK & WHITE IMAGE OF MATLAB

Fig 9. Output JPEG Image after simulation.

#### 13. CONCLUSION

In this paper, we have analyzed the 2-D Discrete Wavelet Transform by using Radix 4-booth multiplier and computational time for the different architectures . This result is useful for converting the RGB image into grey scale image and exploring a new method pipelined of handling multiple data streams suitable for application in image and video processing multimedia real time applications. When down sampling in wavelet transform we need to multiply the row and column with the down sampling factor, this multiplication is being done by the booth multiplier. that is why we are getting better output as compared to Normal Multiplication. Hence the time by normal booth Multiplier is 521225010 ns and time taken by Radix-4 Booth multiplier is 26061000 ns hence near about 50% power reduction than the conventional Normal Booth Multiplier.

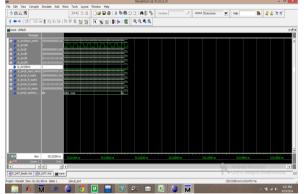

14. SIMULATION RESULT & ANALYSIS 14.1. Simulation Result:

#### 14.2 (c) Simulation on VHDL coding on Model Sim 6.3F of MBA\_DWT algorithm :

Fig 10.4 DWT\_output

### 14.4 (e)Output Result of Simulation using Matlab:

Fig 10.5 Simulation Result.

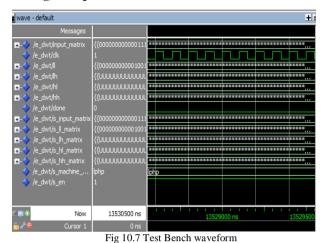

#### 14.5 (g). Output in Test Bench Waveform

#### REFERENCES

- [1] Wei Zhang, Member, IEEE, Zhe Jiang, Zhiyu Gao, and Yanyan Liu, "An Efficient VLSI Architecture for Lifting-Based Discrete Wavelet Transform" IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 59, NO. 3, MARCH 2012.

- [2] Chih-Hsien Hsia, Member, IEEE, Jen-Shiun Chiang, Member, IEEE, and Jing-Ming Guo, Senior Member, IEEE "Memory-Efficient Hardware Architecture of 2-D Dual-Mode Lifting-Based Discrete Wavelet Transform" IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY, VOL. 23, NO. 4, APRIL 2013.

- [3] Jinook Song, Student Member, IEEE, and In-Cheol Park, Senior Member, IEEE, "Pipelined Discrete Wavelet Transform Architecture Scanning Dual Lines" IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 56, NO. 12, DECEMBER 2009.

- [4] Yeong-Kang Lai, Member, IEEE, Lien-Fei Chen, Student Member, IEEE, and Yui-Chih Shih, "A High-Performance and Memory-Efficient VLSI Architecture with Parallel Scanning Method for 2-D Lifting Based Discrete Wavelet Transform" IEEE Transactions on Consumer Electronics, Vol. 55, No. 2, MAY 2009 Contributed Paper.

- [5] Basant Kumar Mohanty, Senior Member, IEEE, and Pramod Kumar Meher, Senior Member, IEEE," Memory-Efficient High-Speed Convolution-based Generic Structure for Multilevel 2-D DWT" IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS FOR VIDEO TECHNOLOGY, VOL. 23, NO. 2, FEBRUARY 2013.

- [6] Yusong Hu, Student Member, IEEE, and Ching Chuen Jong, Member, IEEE, "A Memory-Efficient High-Throughput Architecture for Lifting-Based Multi-Level 2-D DWT" IEEE TRANSACTIONS ON SIGNAL PROCESSING, VOL. 61, NO. 20, OCTOBER 15, 2013..

- [7] Usha Bhanu.N and Dr.A. Chilambuchelvan, "A Detailed Survey on VLSI Architectures for Lifting based DWT for efficient hardware implementation" International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.2, April 2012.

- [8] S. Shafiulla Basha1, Syed. Jahangir Badashah," DESIGN AND IMPLEMENTATION OF RADIX-4 BASED HIGH SPEED MULTIPLIER FOR ALU'S USING MINIMAL PARTIAL PRODUCTS" International Journal of Advances in Engineering & Technology, July 2012. ©IJAET ISSN: 2231-1963.

- [9] G. Jaya Prada, N.C. Pant "Design and Verification of faster Multiplier", vol. 1 issue 3, pp. 683-686, ISSN: 2248-9622. Vol. 1, Issue 3, pp.683-686.

- [10] M. Gopinathan & D. Jessintha (2013) "An Error Compensated DCT Architecture with Booth Multiplier", IJAEEE- ISSN: 2278-8948, Volume-2, Issue-4, 2013.

- [11] Sukhmeet Kaur, Suman and Manpreet Signh Manna," Implementation of Modified Booth Algorithm (Radix 4) and its Comparison with Booth Algorithm (Radix-2)" Advance in Electronic and Electric Engineering. ISSN 2231-1297, Volume 3, Number 6 (2013), pp. 683-690.

- [12] K. Babulu,G. Parasuram, "FPGA Realization of Radix-4 Booth Multiplication Algorithm for High Speed Arithmetic Logics"

(IJCSIT) International Journal of Computer Science and Information Technologies, Vol. 2 (5), 2011, 2102-2107, ISSN:0975-9646.

- [13] Bodasingi Vijay Bhaskar, Valiveti Ravi Tejesvi, Reddi Surya Prakash Rao, "Implementation of Radix-4 Multiplier with a Parallel MAC unit using MBE Algorithm" International Journal of Advanced Research in Computer Engineering & Technology (IJARCET) Volume 1, Issue 5, July 2012, ISSN: 2278 – 1323.

- [14] P. Ramesh, A. Deepthi, K. Sowjanya," Implementation of Discrete Wavelet Transform on FPGA to Detect Electrical Power System Disturbances" International Journal Of Engineering And Computer Science ISSN:2319 7242 Volume 2 Issue 11 November, 2013 Page No. 3223-3227.

- [15] S. JAGADEESH, S.VENKATA CHARY, "Design of Parallel Multiplier–Accumulator Based on Radix-4 Modified Booth Algorithm with SPST" International Journal Of Engineering Research And Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 2, issue 5, September-October 2012, pp.425-431.

- [16] Sakshi Rajput, Priya sharma, Gitanjali and Garima, "High Speed and Reduced Power –Radix-2 Booth Multiplier" (IJCEM) International Journal of Computational Engineering & Management, Vol. 16 Issue 2, March 2013 ISSN (Online): 2230-7893.

- [17] Nishat Bano, "VLSI Design of Low Power Booth Multiplier" International Journal of Scientific & Engineering Research, Volume 3, Issue 2, February -2012 1 ISSN 2229-

#### BIOGRAPHY

**Mr. Hemantkumar H. Nikhare** M.Tech. (Digital & Communication) Scholar in Vedica Institute of Technology Bhopal, under R.G.P.V. Bhopal. And Completed B.E. (Electronics Engg.) from Rajiv Gandhi College of Engineering, Research & Technology Chandrapur under R.T.M.

Nagpur University